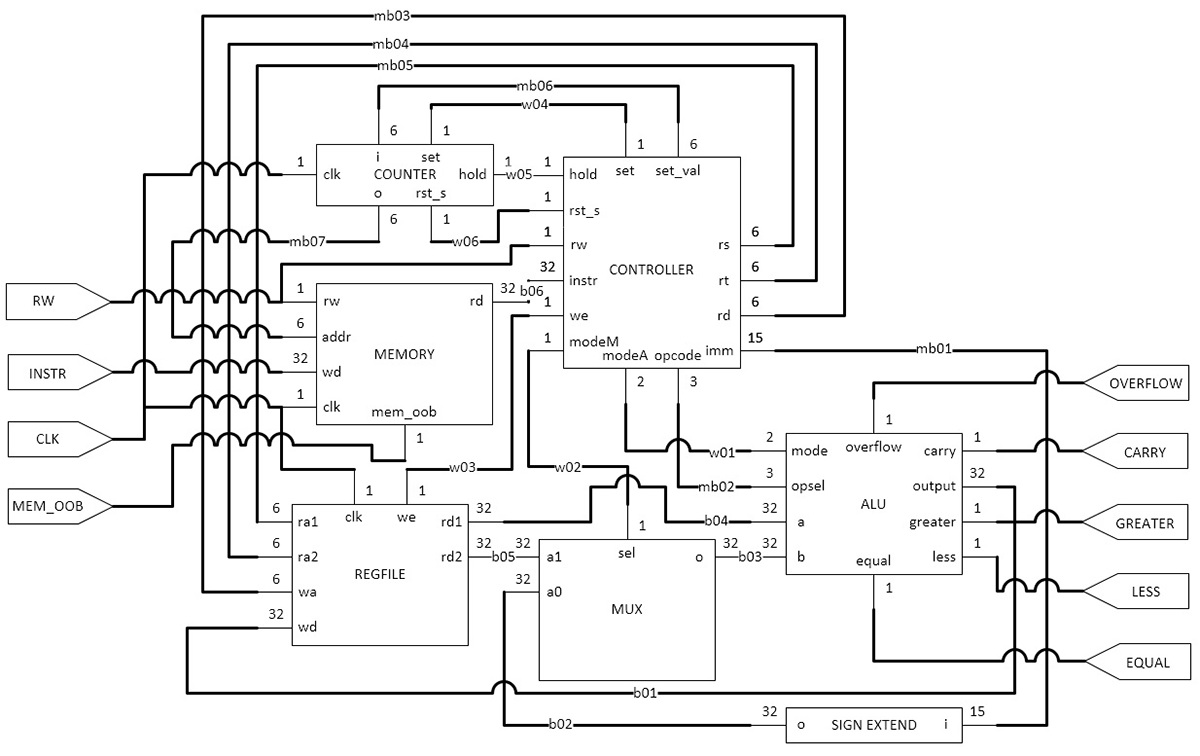

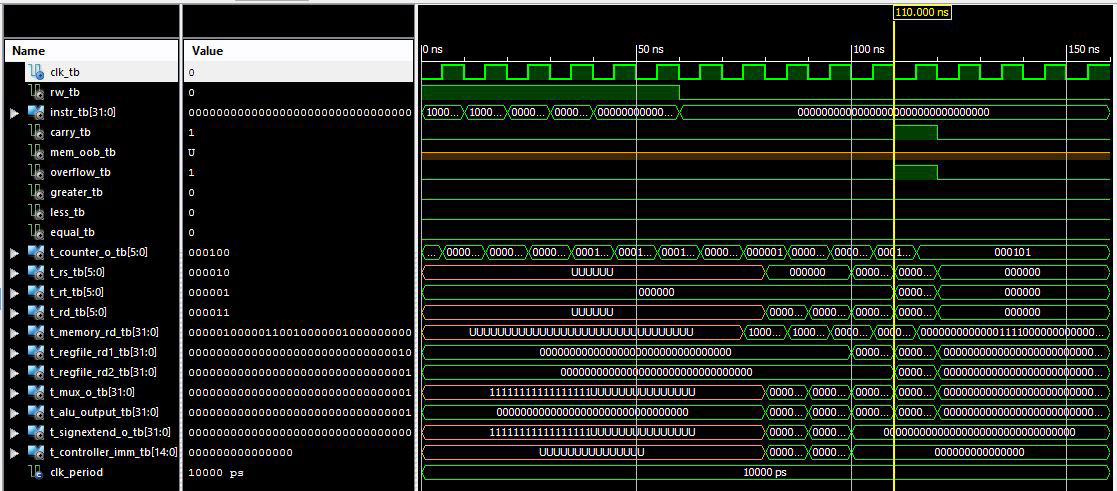

Stage 1: Simple Single-cycle Processor

Initial stages of this build began with a simple single-cycle MIPS processor design. The design supported the following instructions: Add, Subtract, Compare, Bit-wise AND / OR / NOT / XOR, SLL, and Move.

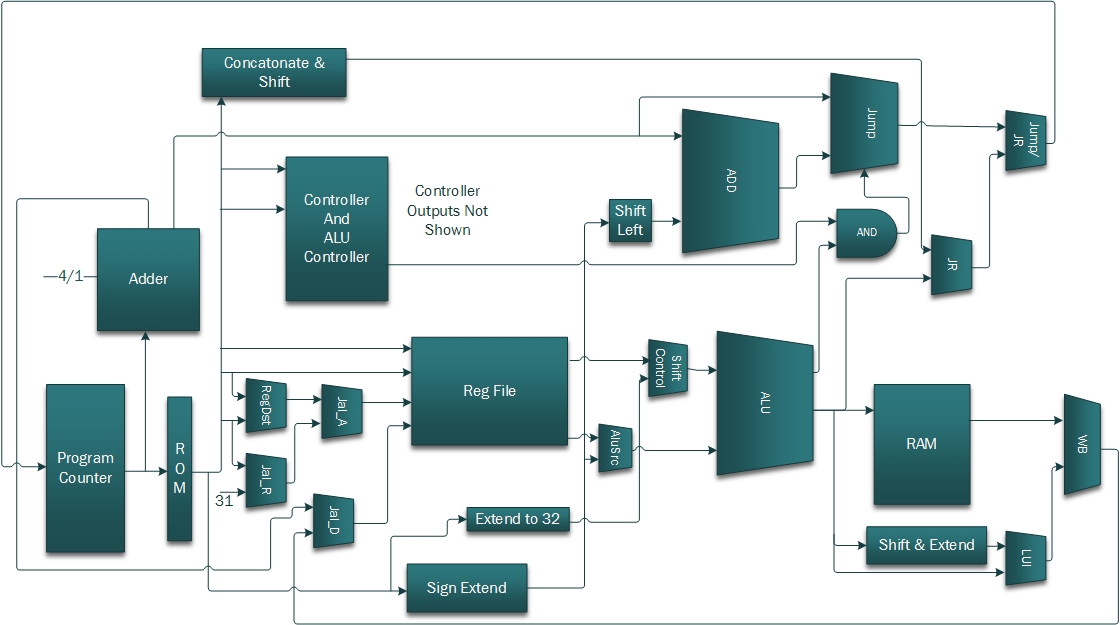

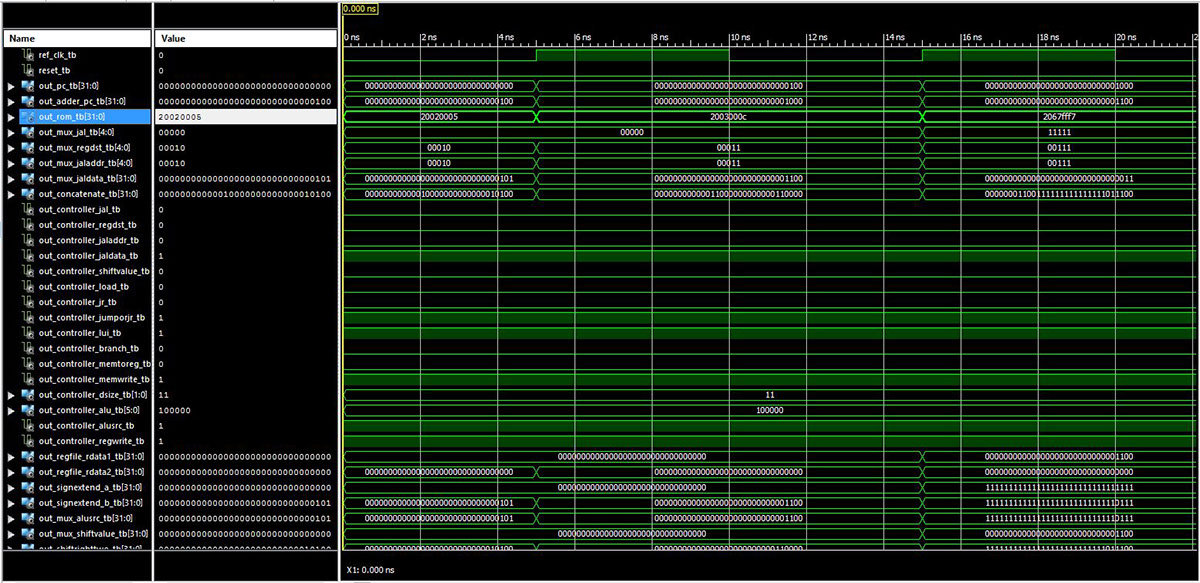

Stage 2: Complex Single-cycle Processor

Stage 2 of this build consisted of expanding the supported instruction set of the previous single-cycle MIPS processor build. This new design supported the following instructions: add, sub, addi, addu, subu, addiu, and, andi, or , ori, nor, xor, xori, sll, srl, sra, sllv, srlv, srav, slt, sltu, slti, sltiu, jump, jal, jr, jalr, beq, bne, bltz, bgez, blez, bgtz, lui, lb, lbu, lh, lhu, lw, sb, sh, and sw.

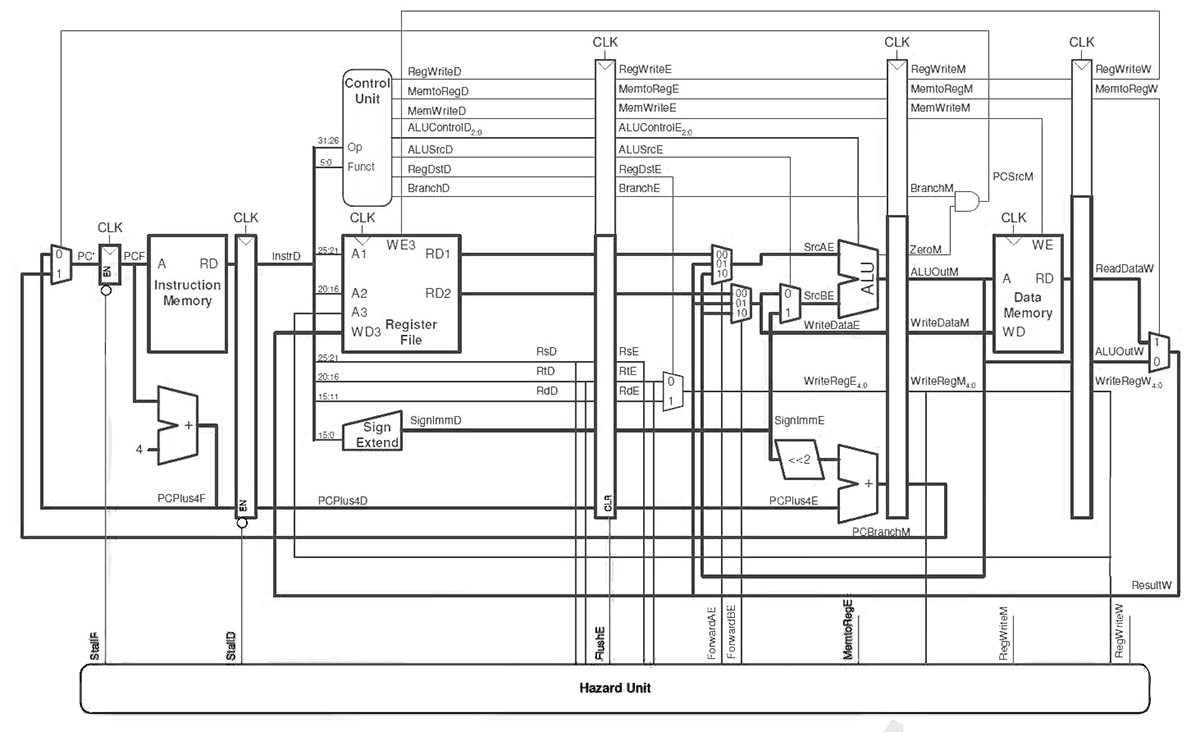

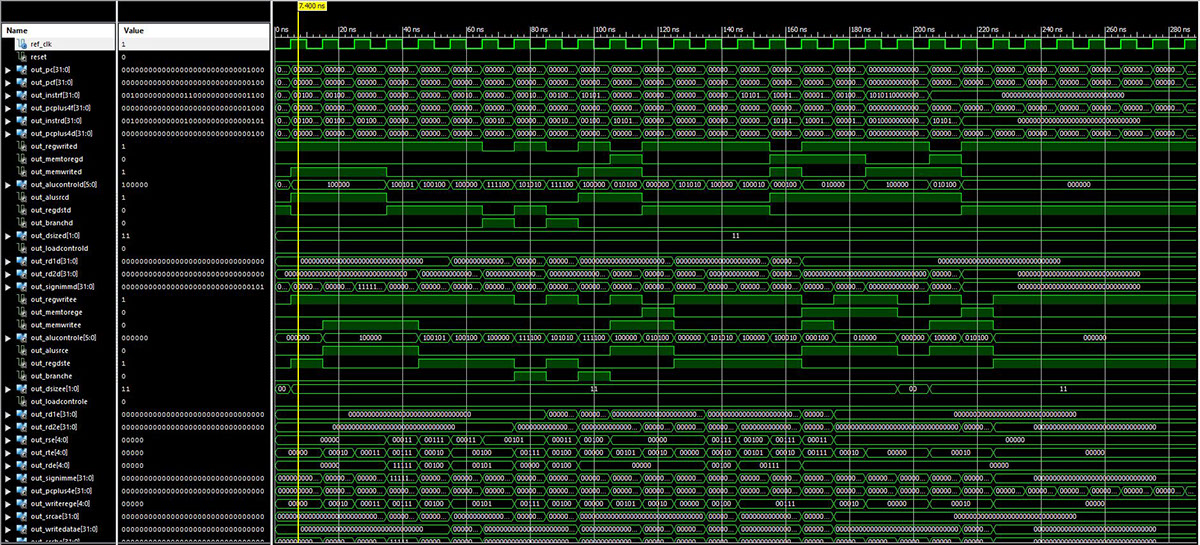

Stage 3: Pipelined Processor

Stage 3 of this build consisted of piplining the previous single-cycle MIPS processor build. Hazard and forwarding logic was also added. After synthesis on both designs, the pipelined design resulted in noticably improved performance metrics.